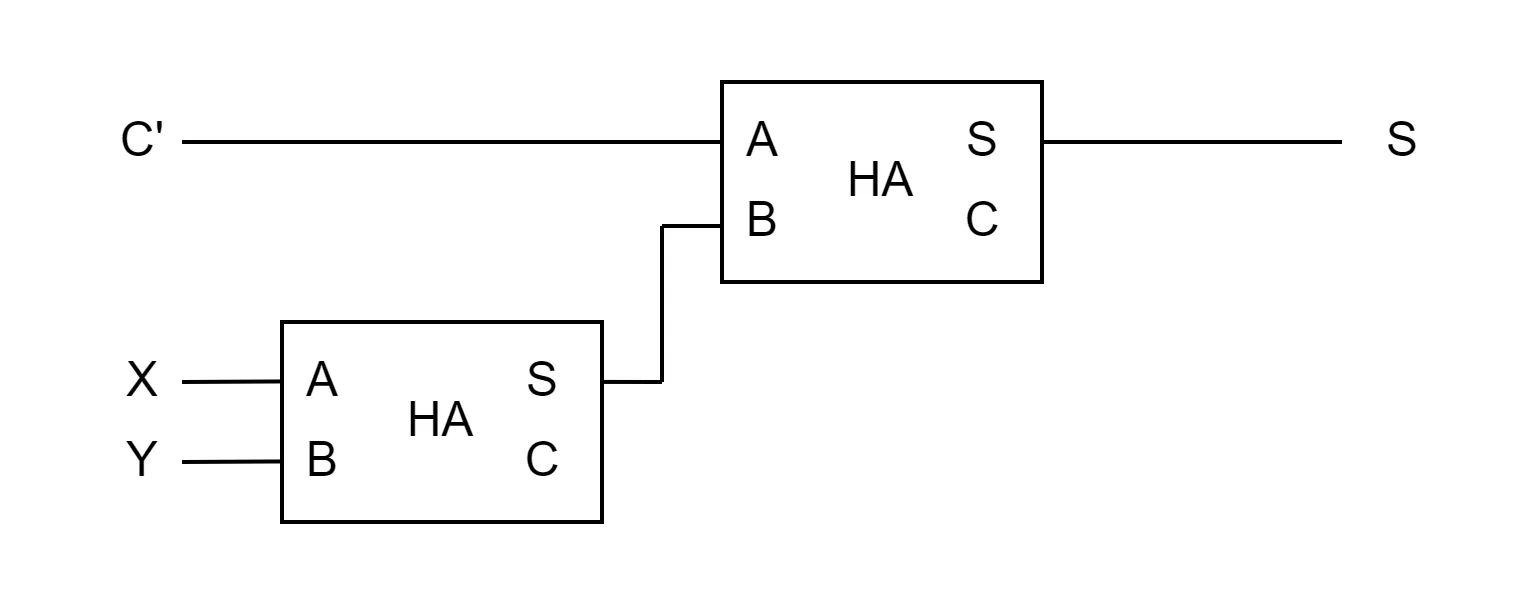

全加算器はサムネイルのように半加算器二つで実装できます。ですが図のシンプルさに対して、その導出過程がなかなかムズイので、メモしておきます。

なにを導出するねんって感じですが、カルノー図から求めた全加算器の入出力関係を、半加算器の入出力関係で表せるように変形するということです。

論理式から導出

まずは半加算器の定義を確認します。半加算器は入力 A, B に対して、出力 S (和), C (桁上げ) を出力します。なお ⊕ は XOR です。

半加算器(A,B)SHACHA=(SHA,CHA)=A⊕B=AB

全加算器は 入力 X, Y, C’ (下位加算器からの桁上げ) に対して、S, C を出力します。次の式は真理値表をもとに、カルノー図を使って簡略化したものです。

全加算器(X,Y,C′)SFACFA=(SFA,CFA)=XˉYˉC′+XˉYC′ˉ+XYC′+XYˉC′ˉ=XY+XC′+YC′

SFA , CFA を SHA, CHA で表すことができれば、全加算器を半加算器で実装できることになります。

まずは SFA から。

SFA=XˉYˉC′+XˉYC′ˉ+XYC′+XYˉC′ˉ=C′(XˉYˉ+XY)+C′ˉ(XˉY+XYˉ)=C′(X⊕Y)+C′ˉ(X⊕Y)=C′⊕X⊕Y=SHA(SHA(X,Y),C′)

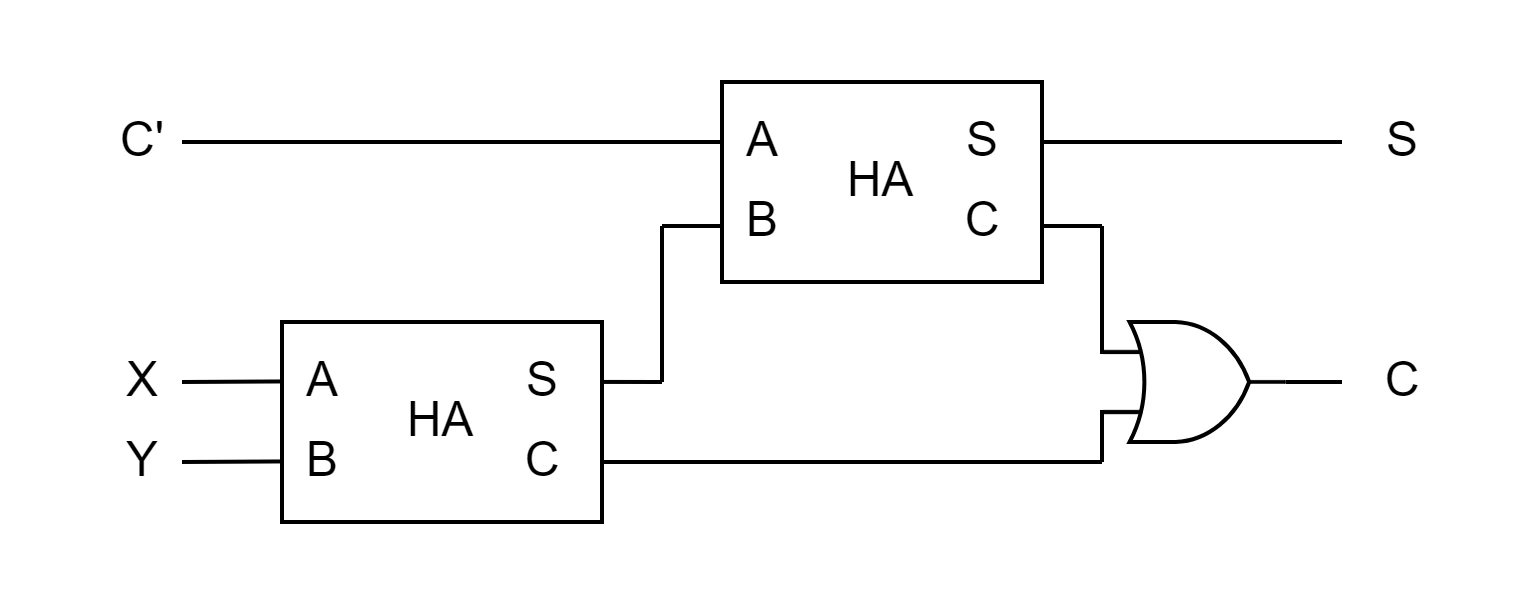

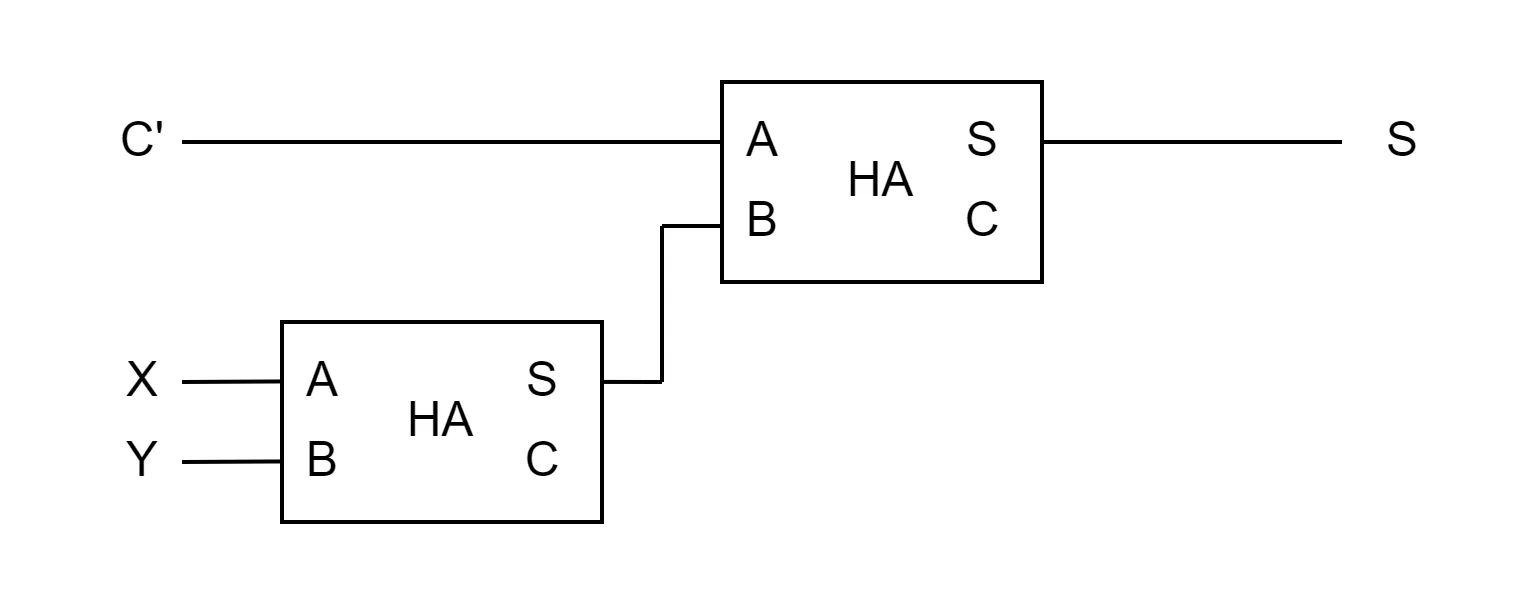

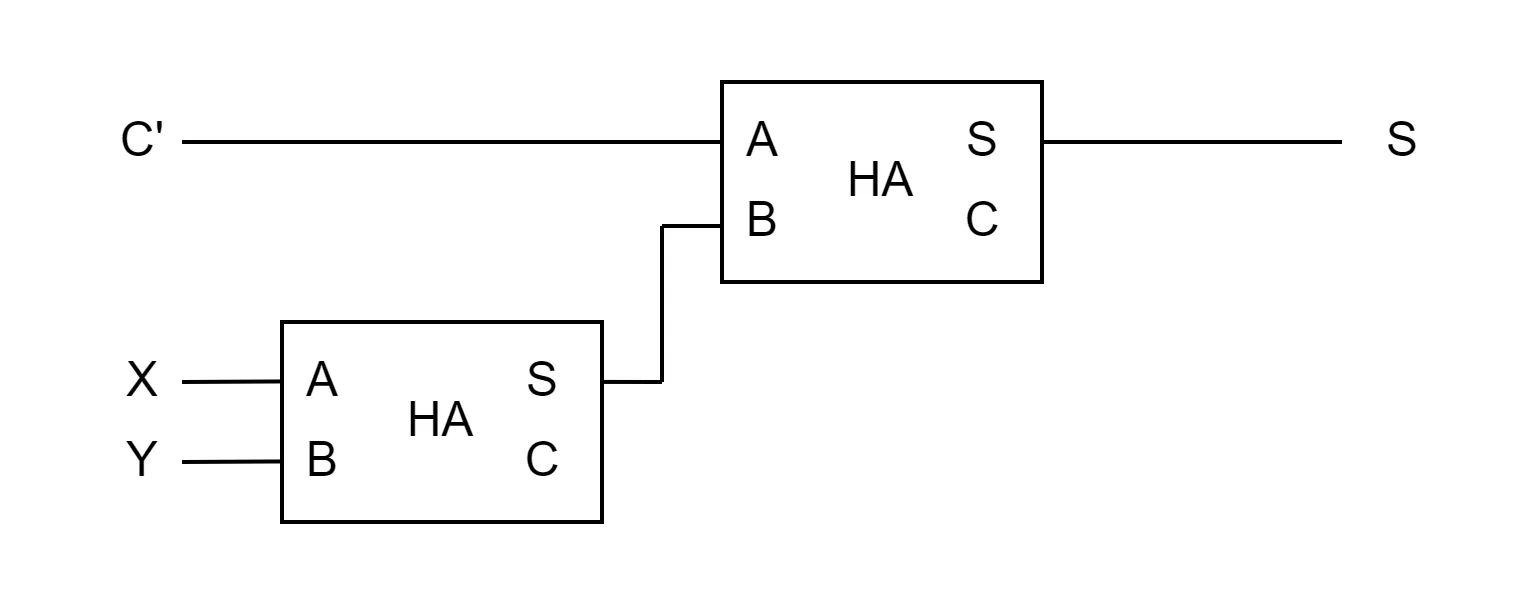

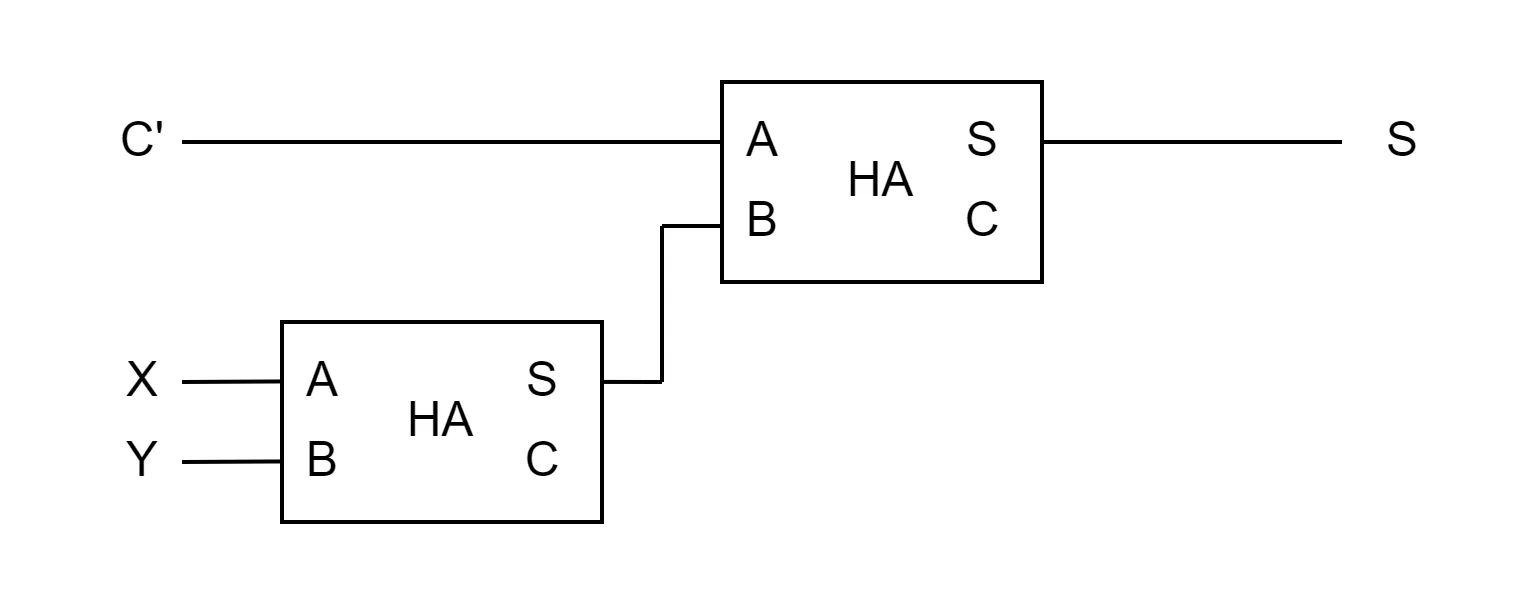

この式は次のように解釈できます。

次に CFA です。これがムズイというか、恣意的な変形が必要です。

CFA=XY+XC′+YC′=XY+XC′+XY+YC′=X(Y+C′)+Y(X+C′)=X(Y+YˉC′)+Y(X+XˉC′)=XY+XYˉC′+YXˉC′=XY+C′(XYˉ+YXˉ)=XY+C′(X⊕Y)=CHA(X,Y)+CHA(SHA(X,Y),C′)

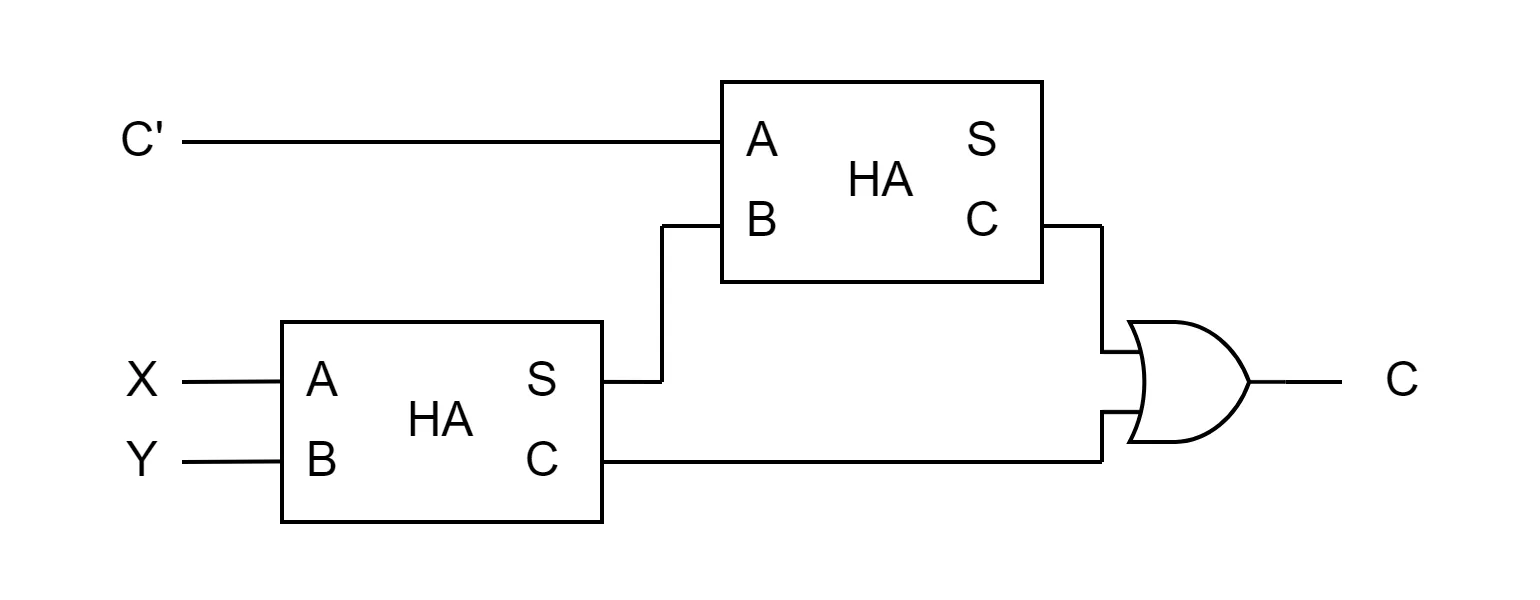

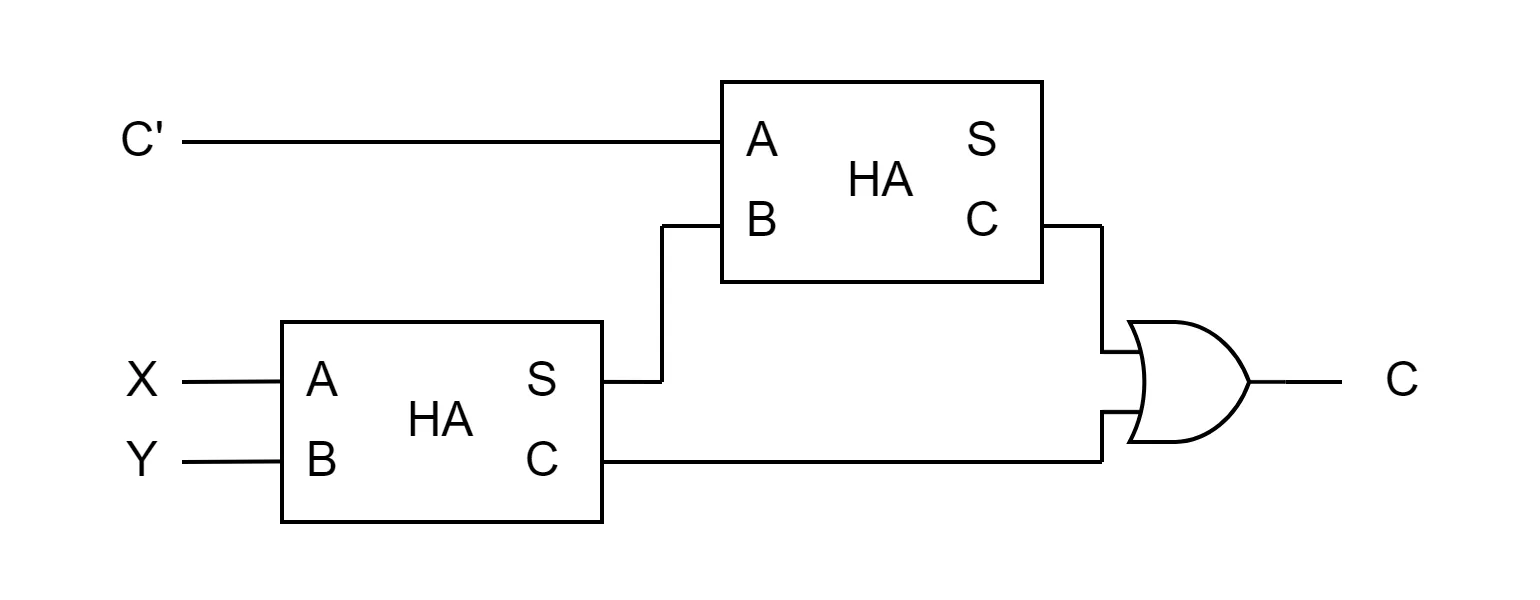

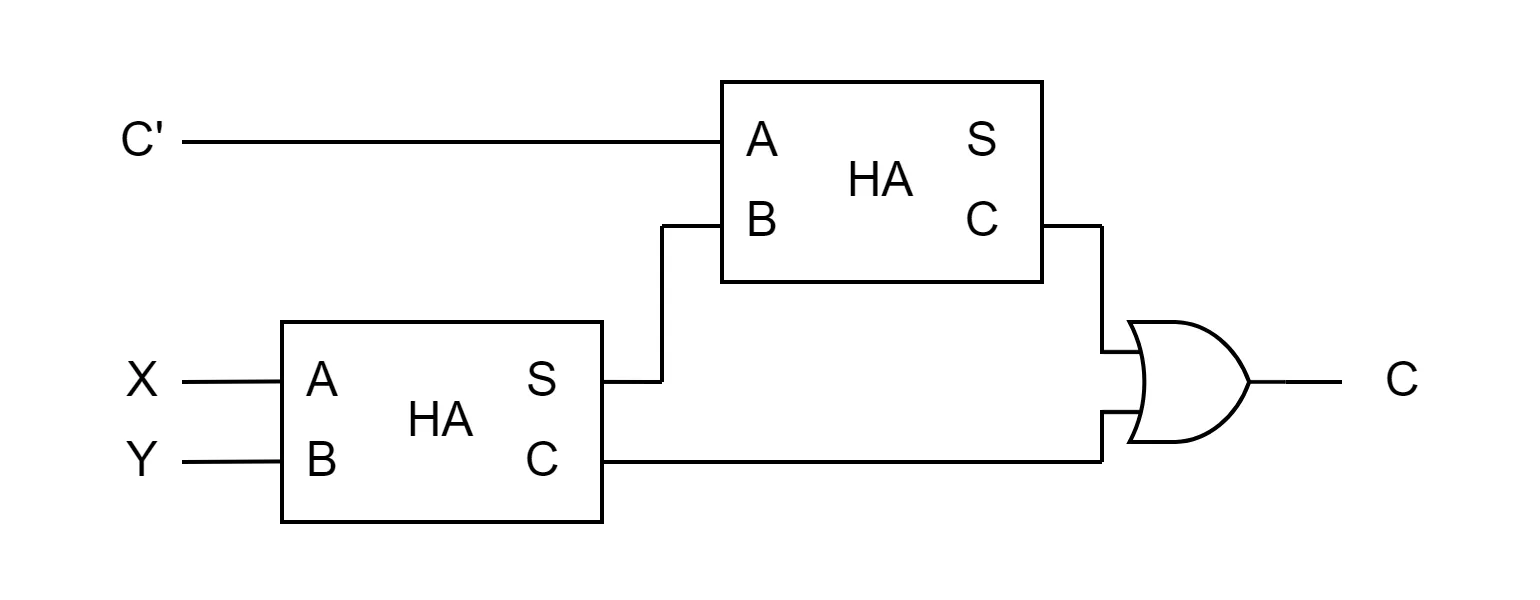

この式は次のように解釈できます。

直感的理解

式変形してカチカチにやってもいいですが、テスト以外で導出するのは流石にやりたくないですし、導出結果をあらかじめイメージできると見直しやすいと思ったので、直感的に理解できるような説明をしておきます。

全加算器は言い換えると 3bit 加算器です。3bit の和は、2bit を加算した結果を残りの 1bit と加算することで求められるので、和の信号は次のようなイメージになります。

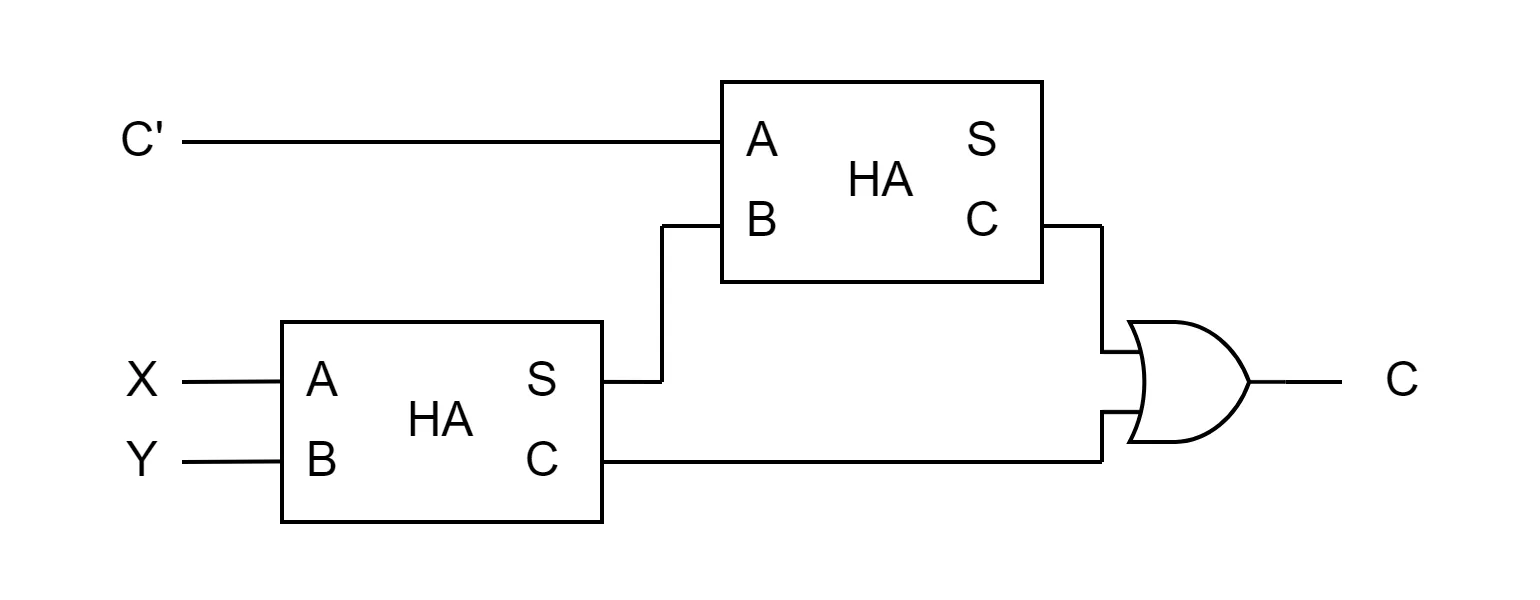

桁上げが発生する条件は、3bit のうち 2bit 以上が 1 の場合です (011, 101, 111 とか)。2bit 以上が 1 になるときには、必ずどちらかの半加算器が桁上げするので、半加算器の桁上げ信号の論理和をとってあげればよいです。次のようなイメージになります。